XCZU47DR

產(chǎn)品型號

ACRF47產(chǎn)地

上海價格

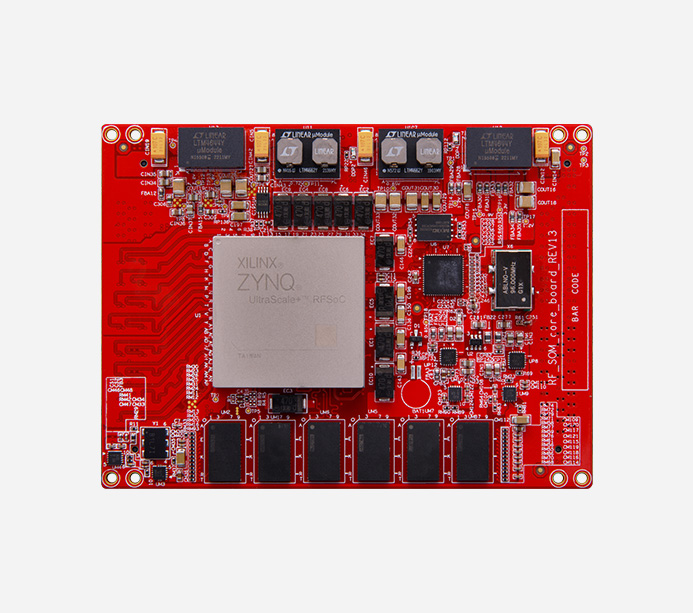

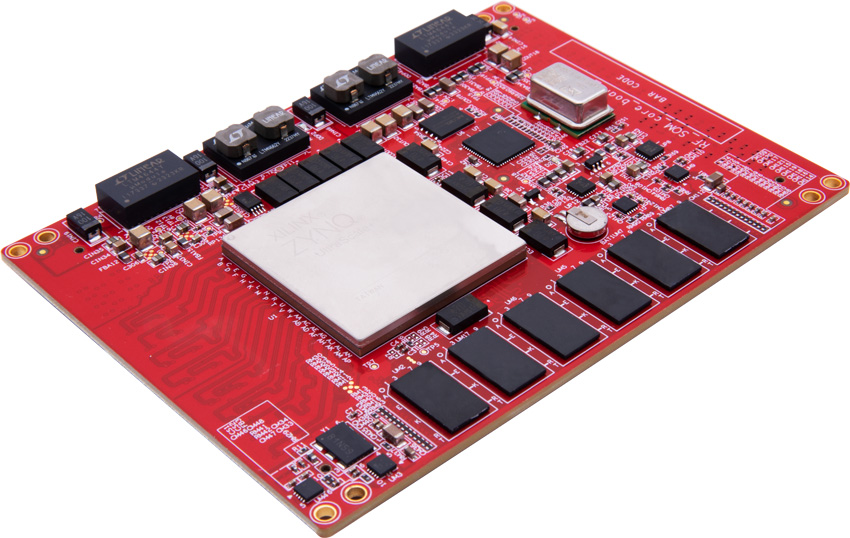

¥85000.00RFSOM 集成硬件和軟件,幫助您提供高性能無線接收器系統(tǒng)的原型,并進(jìn)行空口信號采集和分析。此外 RFSOM 采用射頻直接采樣結(jié)構(gòu),帶有八個獨(dú)立的發(fā)射器和接收器通道。它集成可編程的 Xilinx RFSoC FPGA 最小系統(tǒng),支持軟件無線電開發(fā)架構(gòu),具備大帶寬和大規(guī)模運(yùn)算處理能力,可用于無線通信原型驗(yàn)證、頻譜監(jiān)測、信號智能及寬帶采集記錄等應(yīng)用程序。RFSOM 還配備了19.2 MHz 恒溫晶體振蕩器 (OCXO) 參考時鐘,提高了頻率精度和同步性。

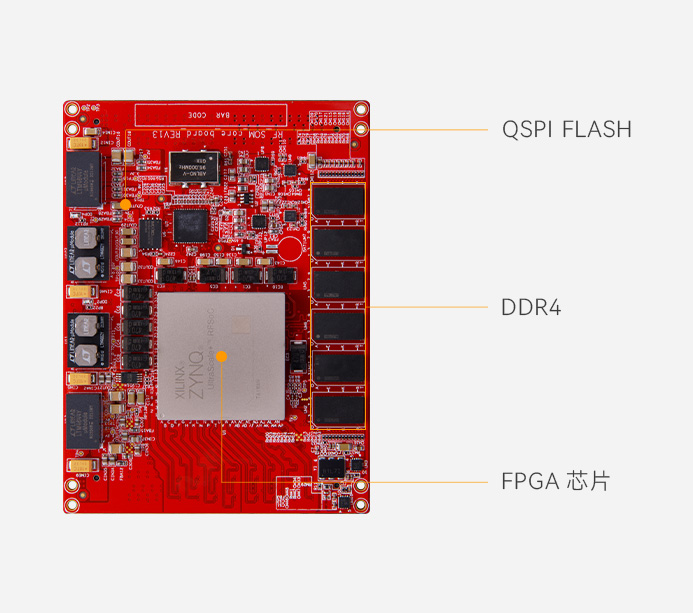

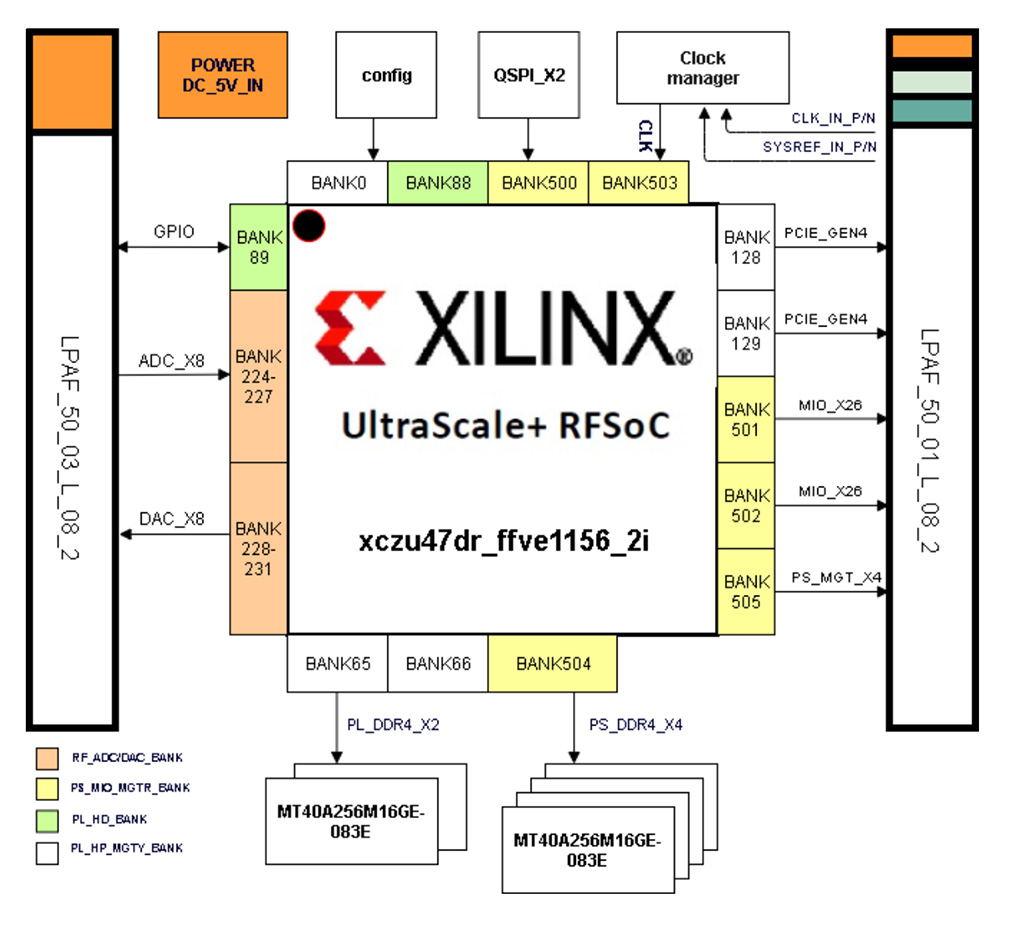

PS 端 DDR4

PL 端 DDR4

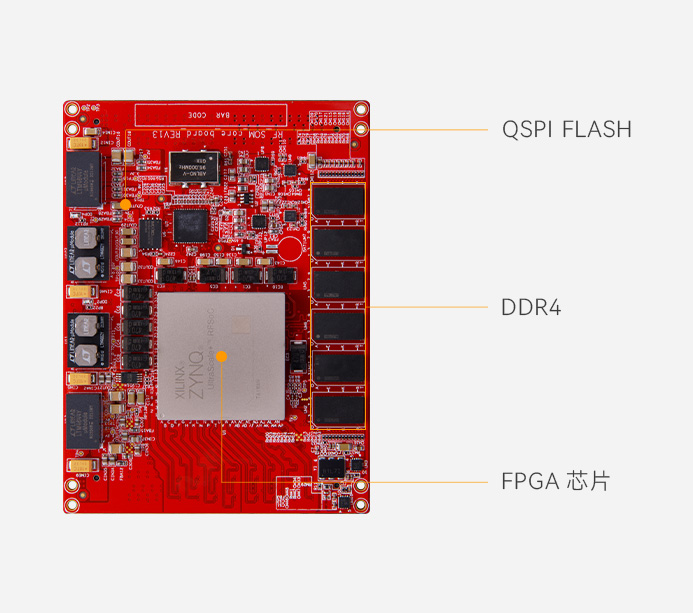

QSPI FLASH

8 個 GTY

8 個 14bit ADC

8 個 14bit DAC

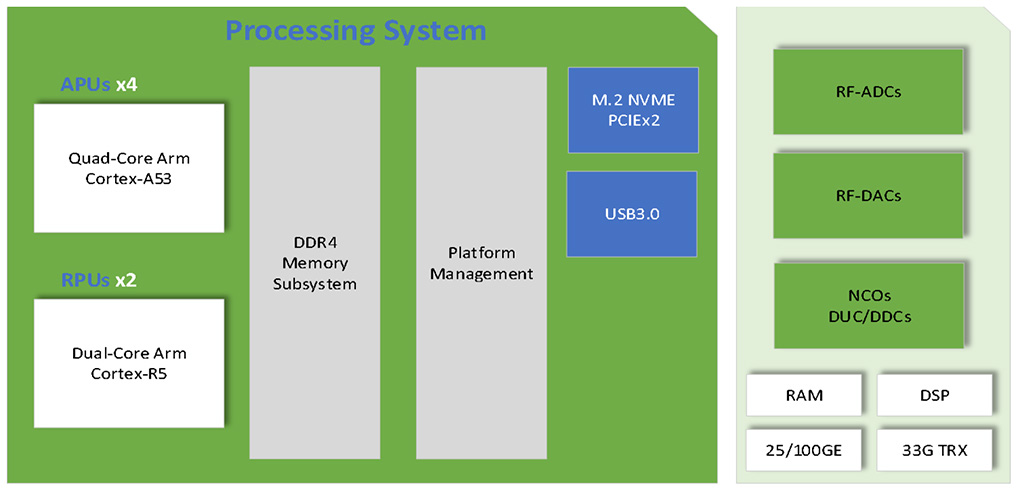

Xilinx Zynq UltraScale+ FPGA 的可編程邏輯部分的 FPGA 資源可提供高吞吐量數(shù)字信號處理 (DSP) 和 IP 核,例如數(shù)字上/下變頻 (DUC/DDC) 內(nèi)核。通過軟件無線電開發(fā)架構(gòu)應(yīng)用程序編程接口和 FPGA 基礎(chǔ)架構(gòu)更容易實(shí)現(xiàn) FPGA 加速。這有助于您快速啟動和運(yùn)行,以便您可以專注于增值 IP。用于快速傅立葉變換 (FFT) 和有限脈沖響應(yīng) (FIR) 濾波器等常用功能的 FPGA 系統(tǒng)是一個很好的起點(diǎn)。然后,您可以使用首選的硬件描述語言 (HDL) 將自己的 IP 塊添加到模塊化架構(gòu)中除了系統(tǒng)的 FPGA 架構(gòu)部分,Xilinx UltraScale+ RFSoC 還配備了四個板載應(yīng)用處理單元 (APU) 和兩個實(shí)時處理單元 (RPU),適用于需要板載嵌入式操作系統(tǒng)進(jìn)行獨(dú)立操作的應(yīng)用

ACRF47 可以支持 AD/DA 通道全差分引出,用戶可根據(jù)需要定義射頻調(diào)理電路,支持直流、交流耦合,支持 PA、LNA 放大器調(diào)理電路。也可以支持選配射頻前端,支持 Lo 變頻器、雙工器、PA、LNA 等。

· ZU47DR 射頻片上系統(tǒng) (RFSoC) 的一體化器件

· 具有內(nèi)置數(shù)字上下變頻和插值抽取功能

· 支持 8 路發(fā)送,8 路接收

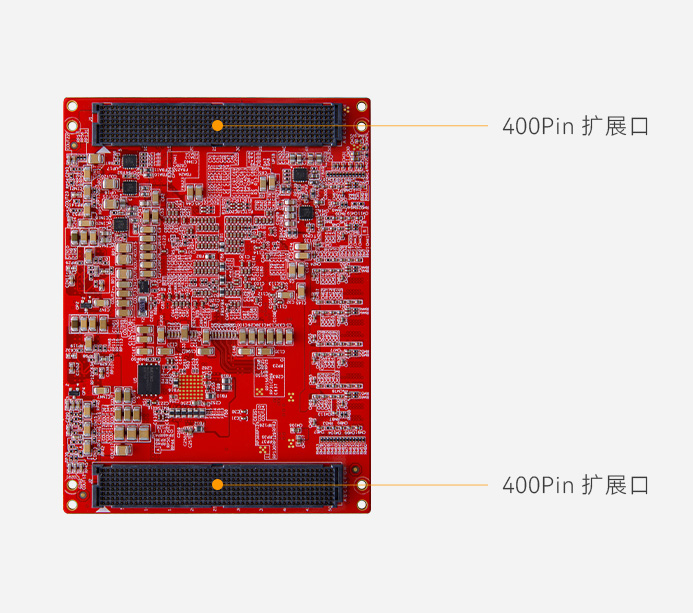

· 模擬RFMC連接器

1. ADC/DAC 全差分引出,支持直流 or 交流耦合

2. VCM 引出支持設(shè)定共模電平

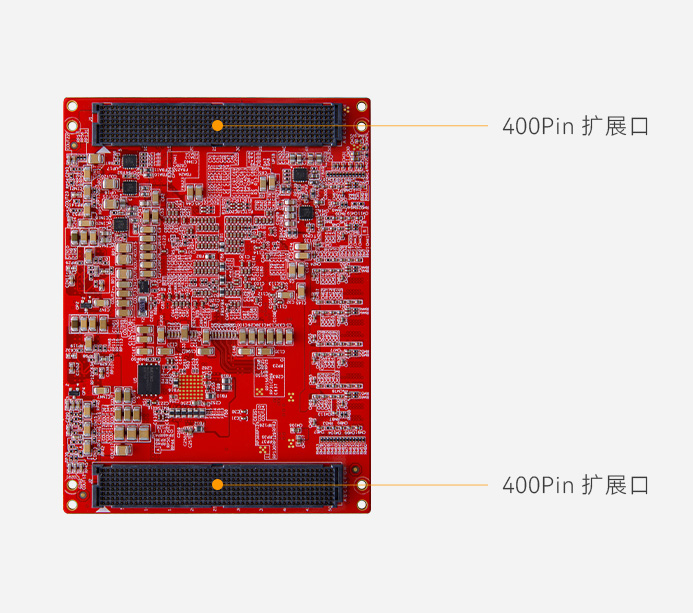

· 數(shù)字 RFMC 連接器

1. GTY 引出,支持 PCIE4.0X8 速率傳輸

2. MIO 引出,支持?jǐn)U展以太網(wǎng)、USB等外設(shè)接口,支持外設(shè)電平

3. GTR 引出,支持?jǐn)U展 sata/pcie 硬盤等存儲接口,支持外設(shè)電平

4. HD IO 引出,支持外設(shè)電平

· 高速緩存

1. PL DDR4 32bit 單通道 DDR4 緩存支持 2600MHz,2GB 容量

2. PS DDR4 64bit 單通道 DDR4 緩存支持 2133MHz,4GB容量

3. QSPI flash,128MB 容量

· 調(diào)試接口

1. JTAG 引出

2. 復(fù)位信號引出

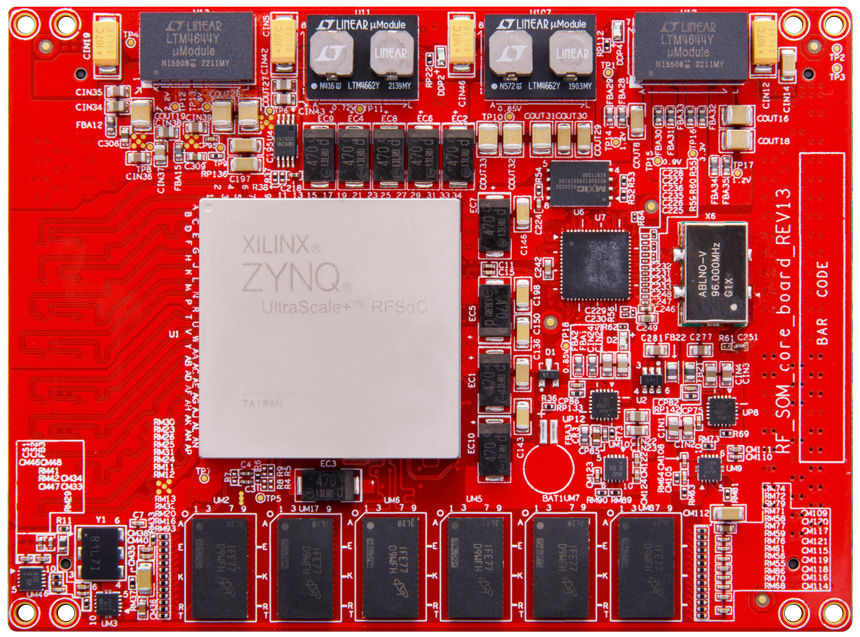

· 內(nèi)建 LMK04828 專用時鐘電路

· 集成 19.2MHz OCXO

· 外時鐘同步

· 觸發(fā)同步

· SYSREF 同步

· 5V 單電源

· 散熱片內(nèi)嵌風(fēng)扇

· 典型功耗,運(yùn)行 50% 邏輯,8TX&8RX,TBD Watt

· API 支持 30.72/61.44/122.88/245.76/491.52/983.04MHz 實(shí)時帶寬(最大可支持 2.5GHz 帶寬)

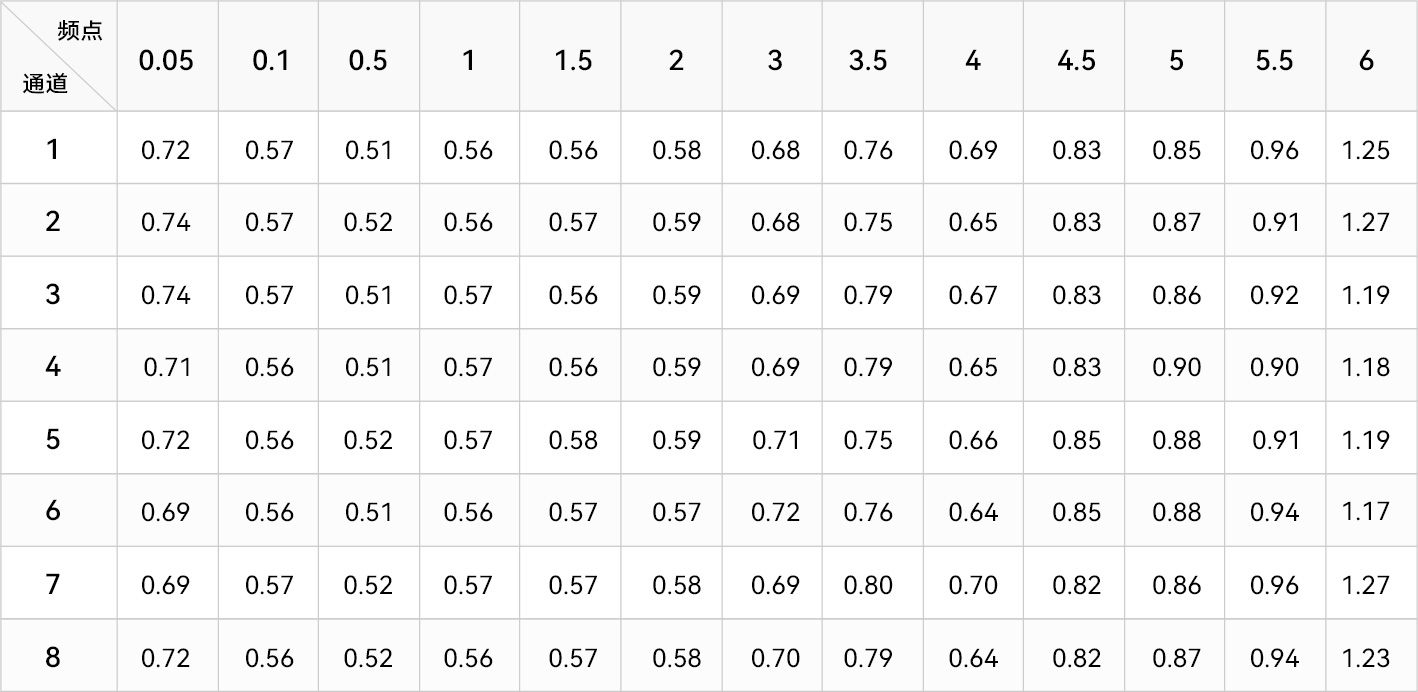

發(fā)射 EVM:典型頻段下,EVM 優(yōu)于 1%

平坦度:1GHz 帶寬下輸出平坦度

相位噪聲

8 個通道的發(fā)射 5GNR 測試結(jié)果如下表所示,5GNR 單位:%rms,頻點(diǎn)單位:GHZ

*對應(yīng)開發(fā)板 AXRF47,點(diǎn)擊了解詳情>>

核心板

ACRF47

FPGA 型號

XCZU47DR-2FFVE1156I

內(nèi)核 CPU

Quad-core ARM Cortex-A53, MPCore

Dual-core ARM Cortex-R5F, MPCore

存儲

PS 端 DDR4,4GB

PL 端 DDR4,2GB

QSPI FLASH 128MB

14 bit 5.0GSPS RF-ADC

8

14 bit 9.85GSPS RF-DAC

8

Decimation/ interpolation

1x, 2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x

GTY / GTR

PL 端 GTY 8 個,PS 端 GTR 4 個

System Logic Cell

930K

CLB LUTs

425K

Max.Dist.RAM

13.0Mb

Total Block RAM

38.0Mb

UltraRAM

22.5Mb

DSP Slices

4272

PCIe Gen4 x8

1

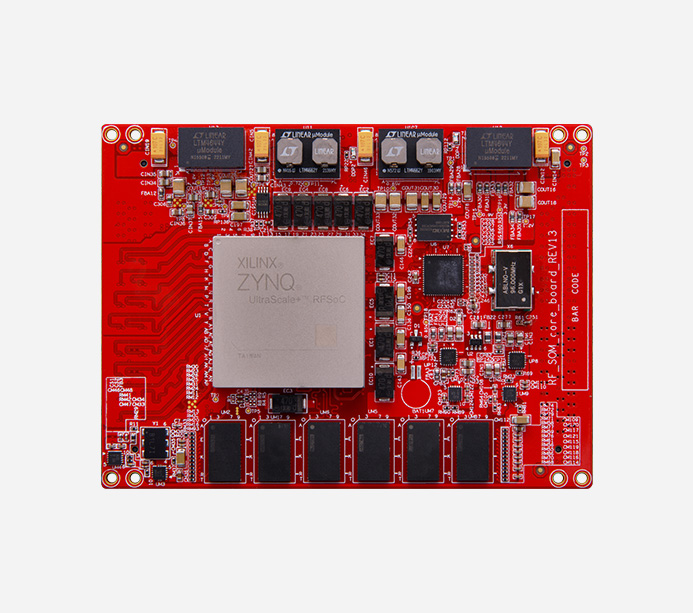

FPGA 核心板

1 塊

尺寸大小

115mmx 85mm

疊層數(shù)量

核心板 14 層 PCB 板設(shè)計,預(yù)留獨(dú)立電源層和 GND 層

核心板結(jié)構(gòu)尺寸圖

通過 Zynq RFSoC,無線基礎(chǔ)設(shè)施制造商可實(shí)現(xiàn)顯著的占板面積及功耗減少,這對 Massive MIMO 部署至關(guān)重要。

Zynq UltraScale+ RFSoC 可幫助有線電視接入多服務(wù)運(yùn)營商 (MSO) 通過遠(yuǎn)程 PHY 節(jié)點(diǎn)將 PHY 層處理移至離家更近的地方,從而可提高網(wǎng)絡(luò)容量。

作為面向可擴(kuò)展、多功能、相控陣?yán)走_(dá)的單芯片 TRX 解決方案,Zynq UltraScale+ RFSoC 能夠在預(yù)警場景下實(shí)現(xiàn)低時延收發(fā),獲得最佳響應(yīng)時間。

設(shè)計人員可通過在 Zynq UltraScale+ RFSoC 中使用直接 RF 采樣、高靈活、可重構(gòu)邏輯及軟件可編程性,為信號生成和信號分析構(gòu)建高速度的多功能儀器。

設(shè)計人員可通過在 Zynq UltraScale+ RFSoC 中使用直接 RF 采樣、高靈活、可重構(gòu)邏輯及軟件可編程性,為信號生成和信號分析構(gòu)建高速度的多功能儀器。

所有出售產(chǎn)品主體保修期為 12 個月,其中 FPGA 芯片、液晶屏為易損件,不在保修范圍內(nèi)。

所有配件及贈品不在保修范圍內(nèi)。

請您補(bǔ)充以下信息,開啟一鍵下載。