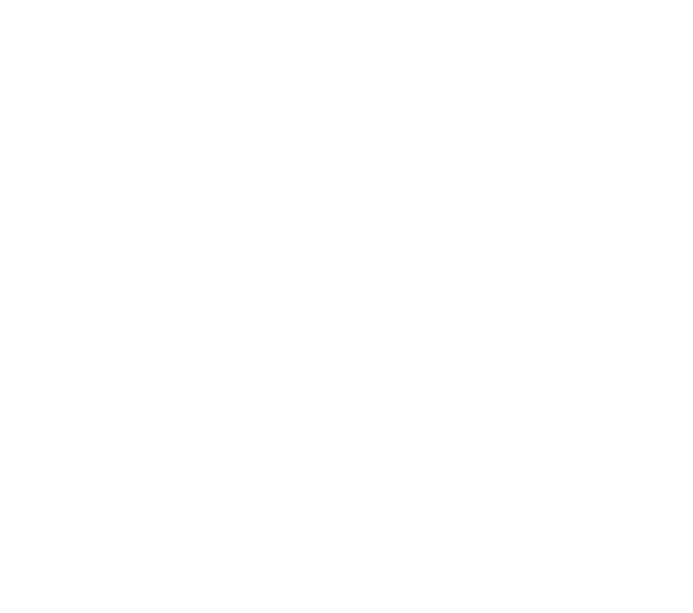

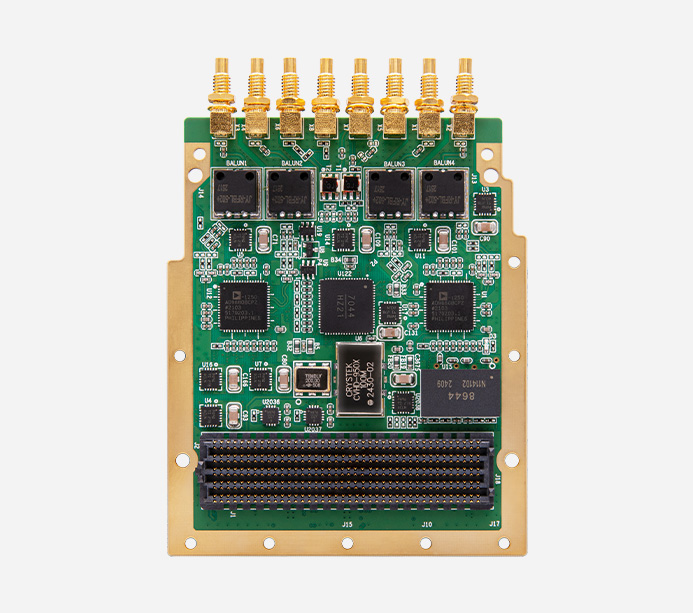

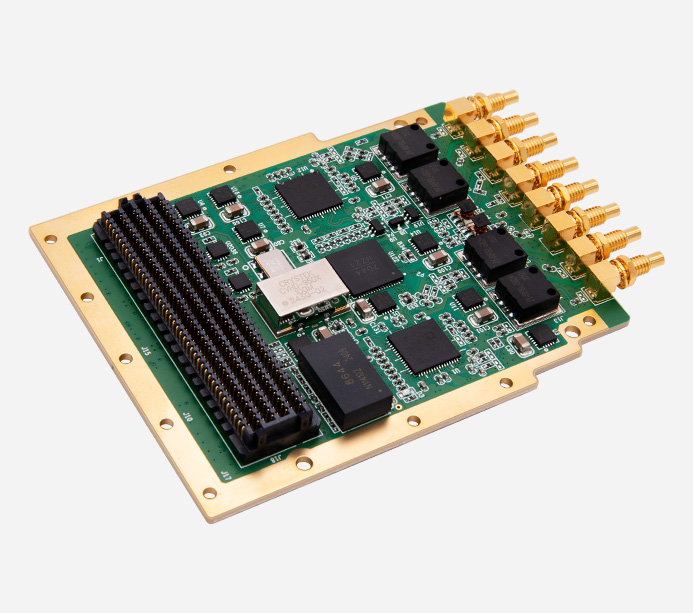

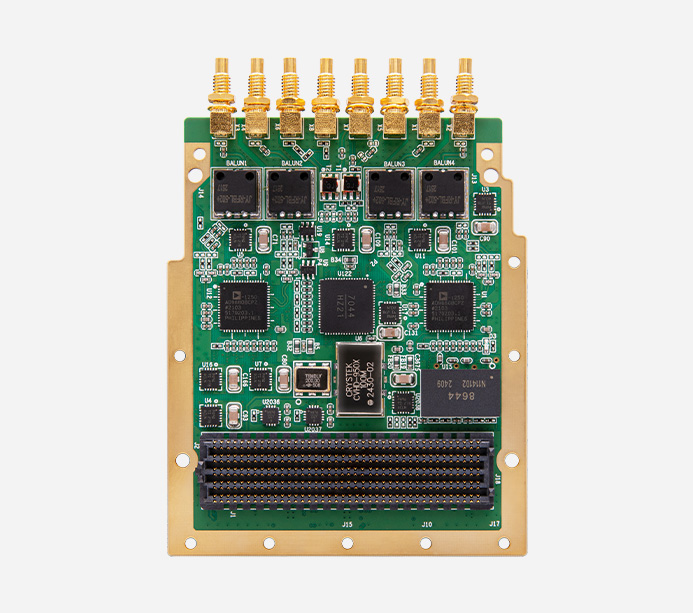

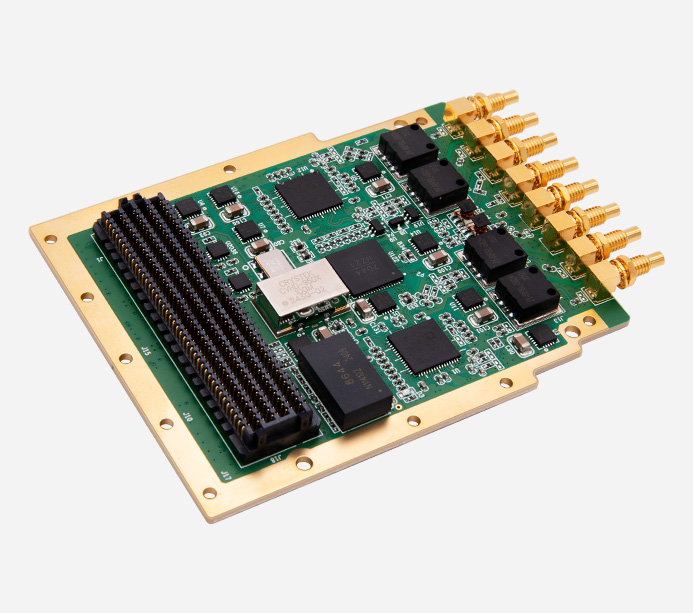

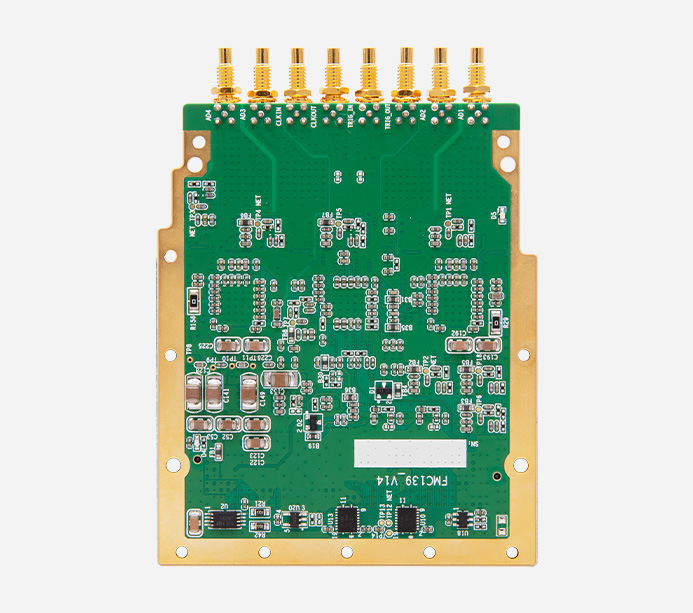

FH9680 基于 VITA57.1 標準規范的 JESD204B 接口 FMC 子卡,該子卡可以實現 4 路 14-bit、1.25GSPS ADC 采集功能。該子卡 ADC 器件采用 ADI 公司的 AD9680 芯片,全功率 -3dB 模擬輸入帶寬可達 2GHz。該 ADC 與 FPGA 的主機接口通過 8 通道的高速串行 GTX 收發器進行互聯

適用于通信與無線基礎設施、雷達、寬頻帶通信、毫米波通信、自動測試設備等應用。

高頻帶寬、低噪聲

8 通道 GTX 收發器互聯

時鐘發生器

工業級可靠

低功耗設計

低噪聲密度

(功能框圖)

接口

JESD204B(子類1)編碼數字輸出

功耗

ARM Mali?-400 MP2

SNR

65.3dBFS@1GHz,-1dBFS amplitude

SFDR

85dBFS@1GHz,-1dBFS amplitude

ENOB

10.8BIT(10MHz)

DNL

±0.5LSB,INL=±2.5LSB

直流供電

1.25V、2.5V,3.3V

噪聲密度

-154dBFS/Hz

無失碼

工作中無丟失的代碼

全功率帶寬

2 GHz (-3 dB)

基準電壓源

ADC內部基準電壓源

通道配置

混合 JESD204B Lane 配置

時鐘發生器

高性能時鐘發生器芯片 HMC7044

時鐘源

支持 100MHz LVDS 晶振,支持外時鐘輸入

觸發

支持1路輸入/輸出觸發信號, LVTTL(3.3V) 電平標準

同步

支持同步輸入/輸出功能

板卡尺寸

84.1 x 69mm

典型功耗

6W

供電

+12V

散熱方式

自然風冷散熱

工作溫度

-40℃~﹢85°C

存儲溫度

-55℃~﹢125°C

工作濕度

5%~95%,非凝結

FMC 子卡

1

該板卡主要面向通信與無線基礎設施、雷達、寬頻帶通信、毫米波通信、自動測試設備等應用

雷達與智能天線

5G及LTE無線技術

自動駕駛

測試與測量

所有出售產品主體保修期為 12 個月,其中 FPGA 芯片、液晶屏為易損件,不在保修范圍內。

所有配件及贈品不在保修范圍內。

請您補充以下信息,開啟一鍵下載。